原料砥粒からスラリーまで一貫生産できる強みを活かし、CMPプロセスに対応したスラリー+研磨ソリューションを提供しています。半導体の多層構造を実現する技術として、SiやSiO2をはじめとした各種ケイ素系材料や配線工程用金属等への高平坦研磨・選択比制御を保有し、半導体前工程・後工程等の各種研磨など様々な研磨要求に応えられるようスラリーの最適化を行っています。

使用用途

- 半導体前工程(ウエハ工程)

- 後工程(パッケージ工程)用の各種研磨

- 研磨対象:酸化膜(SiO2)、Poly-Si膜、窒化膜(SiN)、各種金属、樹脂等

特徴

- 研磨砥粒の設計・製造

- ガラス用研磨剤の技術蓄積

- 各種解析、化学薬液の設計・製造

- 研磨剤評価技術

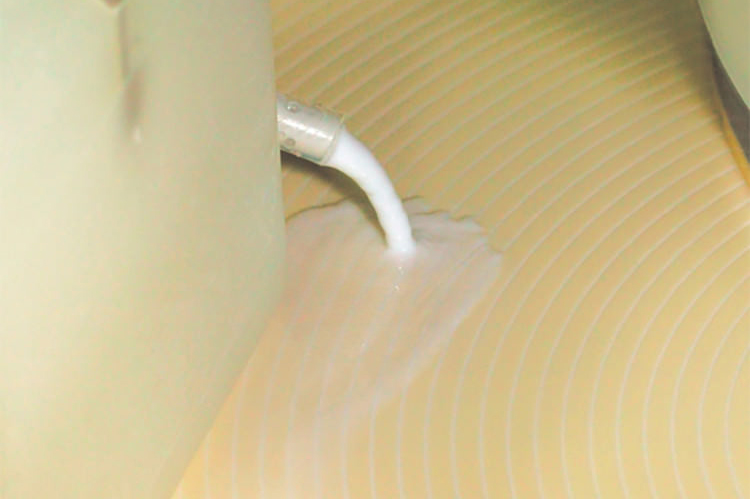

CMP研磨工程

CMP研磨工程

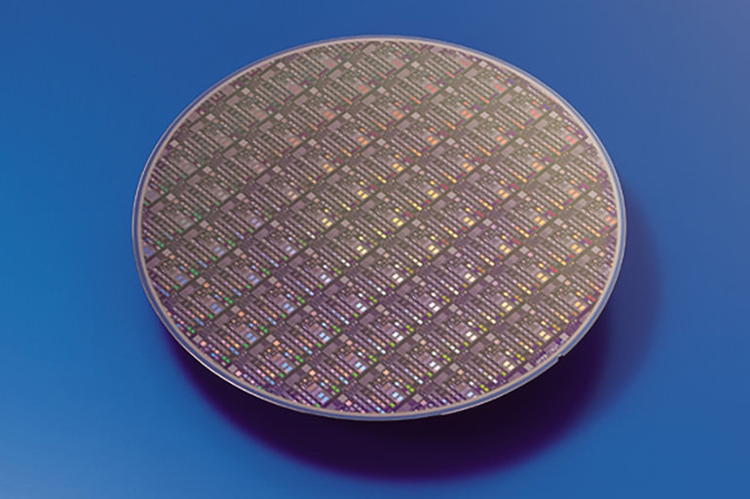

研磨後の8インチウェハー

研磨後の8インチウェハー高度に平坦化された多層構造が実現できます。

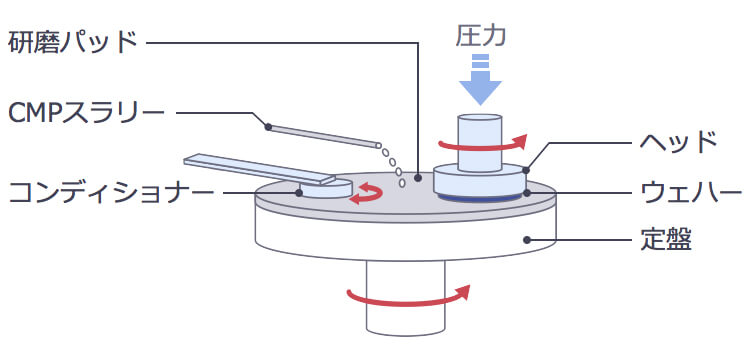

化学的機械的研磨

化学反応によるエッチングと砥粒による機械的研磨を組み合わせた研磨技術で、半導体デバイスの製造工程で配線等による段差を平坦化するプロセスです。「高密度化、高速化」の要求において、素子構造のさらなる多層化が必須です。この時に、平坦化プロセスを採用することにより、優れた半導体素子の実現が可能になります。

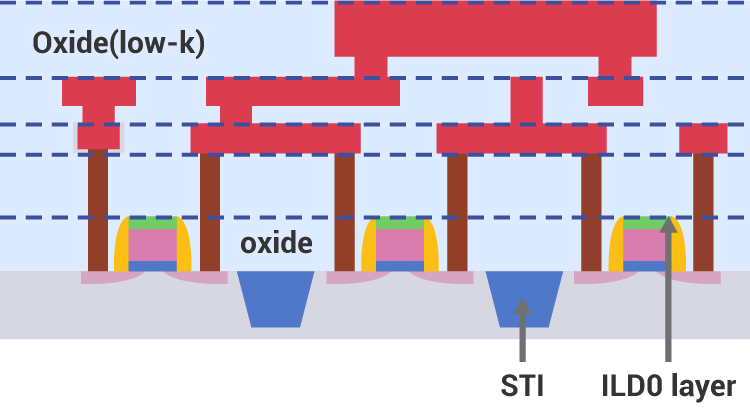

酸化膜研磨用スラリー

CES 330シリーズ/330Fシリーズ/BPシリーズ

・STI用スラリー

・層間絶縁膜用スラリー

シリカ系絶縁膜用には、段差平坦化特性、材料選択性、均一性に優れ、且つ、ディフェクト発生の少ない高機能セリアスラリーを研磨条件含めて 素材ソリューションとして提供しています。 さらに、一液、二液のどちらでも供給可能です。